EDA实验数字时钟(EDA课程设计——数字电子钟)

1.EDA课程设计——数字电子钟

这里说得很详细: 参考资料:

给你发一段

数码管的扫描显示:LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; -字模输出模块

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY SEL IS PORT(CLK:IN STD_LOGIC; Q:OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); --输入选通信号END SEL;ARCHITECTURE SELA OF SEL ISBEGIN PROCESS(CLK) VARIABLE CNT:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN IF CLK'EVENT AND CLK='1' THEN CNT:=CNT+1; END IF; Q

2.EDA设计数字时钟

2. 微秒模块 采用VHDL语言输入方式,以时钟clk,清零信号clr以及暂停信号STOP为进程敏感变量,程序如下:library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity MINSECONDb is port(clk,clrm,stop:in std_logic;----时钟/清零信号 secm1,secm0:out std_logic_vector(3 downto 0);----秒高位/低位 co:out std_logic);-------输出/进位信号 end MINSECONDb; architecture SEC of MINSECONDb is signal clk1,DOUT2:std_logic; begin process(clk,clrm) variable cnt1,cnt0:std_logic_vector(3 downto 0);---计数 VARIABLE COUNT2 :INTEGER RANGE 0 TO 10 ; begin IF CLK'EVENT AND CLK='1'THEN IF COUNT2>=0 AND COUNT2<10 THEN COUNT2:=COUNT2+1; ELSE COUNT2:=0; DOUT2<= NOT DOUT2; END IF; END IF; if clrm='1' then----当clr为1时,高低位均为0 cnt1:="0000"; cnt0:="0000"; elsif clk'event and clk='1' then if stop='1' then cnt0:=cnt0; cnt1:=cnt1; end if; if cnt1="1001" and cnt0="1000" then----当记数为98(实际是经过59个记时脉冲) co<='1';----进位 cnt0:="1001";----低位为9 elsif cnt0<"1001" then----小于9时 cnt0:=cnt0+1;----计数--elsif cnt0="1001" then--clk1<=not clk1; else cnt0:="0000"; if cnt1<"1001" then----高位小于9时 cnt1:=cnt1+1; else cnt1:="0000"; co<='0'; end if; end if; end if; secm1<=cnt1; secm0<=cnt0; end process; end SEC;3. 秒模块程序清单 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity SECOND is port(clk,clr:in std_logic;----时钟/清零信号 sec1,sec0:out std_logic_vector(3 downto 0);----秒高位/低位 co:out std_logic);-------输出/进位信号 end SECOND; architecture SEC of SECOND is begin process(clk,clr) variable cnt1,cnt0:std_logic_vector(3 downto 0);---计数 begin if clr='1' then----当ckr为1时,高低位均为0 cnt1:="0000"; cnt0:="0000"; elsif clk'event and clk='1' then if cnt1="0101" and cnt0="1000" then----当记数为58(实际是经过59个记时脉冲) co<='1';----进位 cnt0:="1001";----低位为9 elsif cnt0<"1001" then----小于9时 cnt0:=cnt0+1;----计数 else cnt0:="0000"; if cnt1<"0101" then----高位小于5时 cnt1:=cnt1+1; else cnt1:="0000"; co<='0'; end if; end if; end if; sec1<=cnt1; sec0<=cnt0; end process; end SEC;4. 分模块程序清单 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity MINUTE is port(clk,en:in std_logic; min1,min0:out std_logic_vector(3 downto 0); co:out std_logic); end MINUTE; architecture MIN of MINUTE is begin process(clk) variable cnt1,cnt0:std_logic_vector(3 downto 0); begin if clk'event and clk='1' then if en='1' then if cnt1="0101" and cnt0="1000" then co<='1'; cnt0:="1001"; elsif cnt0<"1001" then cnt0:=cnt0+1; else cnt0:="0000"; if cnt1<"0101" then cnt1:=cnt1+1; else cnt1:="0000"; co<='0'; end if; end if; end if; end if; min1<=cnt1; min0<=cnt0; end process; end MIN;5. 时模块程序清单 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity HOUR is port(clk,en:in std_logic;----输入时钟/高电平有效的使能信号 h1,h0:out std_logic_vector(3 downto 0));----时高位/低位 end HOUR; architecture hour_arc of HOUR is begin process(clk) variable cnt1,cnt0:std_logic_vector(3 downto 0);----记数 begin if clk'event and clk='1' then---上升沿触发 if en='1' then---同时“使能”为1 if cnt1="0010" and cnt0="0011" then cnt1:="0000";----高位/低位同时为0时 cnt0:="0000"; elsif cnt0<"1001" then----低位小于9时,低位记数累加 cnt0:=cnt0+1; else cnt0:="0000"; cnt1:=cnt1+1;-----高位记数累加 end if; end if; end if; h1<=cnt1; h0<=cnt0; end process; end hour_arc; 6. 动态扫描模块 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity SELTIME is port( clk:in std_logic;------扫描时钟 secm1,secm0,sec1,sec0,min1,min0,h1,h0:in std_logic_vector(3 downto 0);-----分别为秒个位/时位;分个位/ daout:out std_logic_vector(3 downto 0);----------------输出 sel:out std_logic_vector(2 downto 0));-----位选信号 end SELTIME; architecture fun of SELTIME is signal count:std_logic_vector(2 downto 0);----计数信号 begin sel="111") then count<="000"; else countdaoutdaoutdaoutdaoutdaoutdaoutdaoutdaout<=h1; end case; end process; end fun;7. 报时模块 library ieee; use ieee.std_logic_1164.all; 。

3.eda 数字时钟

我不是学姐,答案我就不帮你做了,给你一些提示,希望你能独立完成。

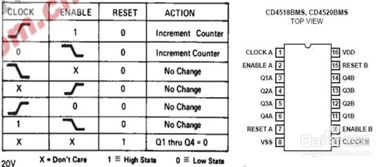

1:先选对计数器,根据需要选择4位,8位,32位(如果没有32位的计数器可以用2个16位的计数器级联起来,第一级的计数器的高位输出驱动第二级的计数器始终)2:10进制,12进制,60进制的计数器怎么做?你需要一个比较器,比较器输入端比较counter的值和一个preset value,如果两个值相等,则输出一,否则输出0,用这个比较信号来控制counter的复位信号,注意有些复位是低电平有效3:有了上面的这些计数器以后怎么做时钟?用级联的方式把上面这些计数器串联起来,也就是说用function generator 产生一个10Hz的频率分秒的比较器输出当作秒的时钟输入(enable也可以),同样的道理,秒的计数器的比较器出入做分的计数器的十种输入。

4.eda 数字时钟

我不是学姐,答案我就不帮你做了,给你一些提示,希望你能独立完成。

1:先选对计数器,根据需要选择4位,8位,32位(如果没有32位的计数器可以用2个16位的计数器级联起来,第一级的计数器的高位输出驱动第二级的计数器始终)

2:10进制,12进制,60进制的计数器怎么做?

你需要一个比较器,比较器输入端比较counter的值和一个preset value,如果两个值相等,则输出一,否则输出0,用这个比较信号来控制counter的复位信号,注意有些复位是低电平有效

3:有了上面的这些计数器以后怎么做时钟?

用级联的方式把上面这些计数器串联起来,也就是说

用function generator 产生一个10Hz的频率分秒的比较器输出当作秒的时钟输入(enable也可以),同样的道理,秒的计数器的比较器出入做分的计数器的十种输入。

相关推荐

声明:本网站尊重并保护知识产权,根据《信息网络传播权保护条例》,如果我们转载的作品侵犯了您的权利,请在一个月内通知我们,我们会及时删除。

蜀ICP备2020033479号-4 Copyright © 2016 学习鸟. 页面生成时间:2.555秒